# MOSFETs Kizito NKURIKIYEYEZU, Ph.D.

# Introduction

- Transistors are three-terminal devices —unlike diodes, which have only two

- The basic usage of a transistor is the ability to use the voltage between two terminals to control the current flowing in the third terminal

- They are more useful because they present multitude of applications: signal amplification, digital logic, memory, etc...

- There are two major types of three-terminal semiconductor devices:

- BJT—bipolar junction transistor

- MOSFET—metal oxide-semiconductor field-effect transistor

- MOSFETs are considered preferable to BJT technology for many applications and are much widely used because:

- size (smaller)

- ease of manufacture

- lesser power utilization

June 29, 2022 1 / 2

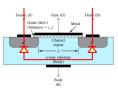

# **MOSFET structure**

- two n-type doped regions (drain, source), and one p-type doped region

- layer of SiO<sub>2</sub> separates source and drain

- metal, placed on top of SiO<sub>2</sub>, forms gate electrode

- Four terminals: the gate(G), the source (S), the drain (D) and the Body (B).

#### FIG 1. Physical structure of the enhancement-type NMOS transistor.

Typically  $L=0.03\,\mu m$  to  $1\,\mu m,\,W=0.05\,\mu m$  to 100  $\mu m,$  and the thickness of the oxide layer (tox) is in the range of 1 to 10 nm.

| Kizito NKURIKIYEYEZU, Ph.D. | MOSFETs | June 29, 2022 2 / 25 | Kizito NKURIKIYEYEZU, Ph.D. | MOSFE' |

|-----------------------------|---------|----------------------|-----------------------------|--------|

# Operations with zero gate voltage

- With zero voltage applied to gate, two back-to-back diodes exist in series between drain and source.

- These diodes prevent current conduction from drain to source when a voltage v<sub>DS</sub> is applied.

- In short, the path between drain and source has a very high resistance (of the order of 10 TΩ.

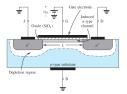

# Creating a channel for current flow

What would happen if (1) the source and drain are grounded and (2) a positive voltage is applied to gate ?

FIG 2. The enhancement-type NMOS transistor with a positive voltage applied to the gate. An n-channel is induced at the top of the substrate beneath the gate.

# Creating a channel for current flow

- Step 1—*v*<sub>GS</sub> is applied to the gate terminal, causing a positive build up of positive charge along metal electrode.

- Step 2—This "build up" causes free holes to be repelled from region of p-type substrate under gate.

FIG 3. The enhancement-type NMOS transistor with a positive voltage applied to the gate. An n-channel is induced at the top of the substrate beneath the gate.

| 4                           |         |               |      |                             |         |                      |

|-----------------------------|---------|---------------|------|-----------------------------|---------|----------------------|

| Kizito NKURIKIYEYEZU, Ph.D. | MOSFETs | June 29, 2022 | 4/25 | Kizito NKURIKIYEYEZU, Ph.D. | MOSFETs | June 29, 2022 5 / 25 |

# Creating a channel for current flow

- Step 1—v<sub>GS</sub> is applied to the gate terminal, causing a positive build up of positive charge along metal electrode.

- Step 2—This "build up" causes free holes to be repelled from region of p-type substrate under gate.

- Step 3—This "migration" results in the uncovering of negative bound charges, originally neutralized by the free holes

- Step 4—The positive gate

FIG 4. The enhancement-type NMOS transistor with a positive voltage applied to the gate. An n-channel is induced at the top of the substrate beneath the gate.

# Creating a channel for current flow

- Step 5—Once a sufficient number of these electrons accumulate, an n-region is created and connects the source and drain regions

- Step 6—This provides path for current flow between D and S.

- Note: This induced channel is also known as an inversion layer

FIG 5. The enhancement-type NMOS transistor with a positive voltage applied to the gate. An n-channel is induced at the top of the substrate beneath the gate.

#### June 29, 2022 6 / 25

#### Kizito NKURIKIYEYEZU, Ph.D.

### Creating a channel for current flow

- threshold voltage Vt<sup>1</sup> is the minimum value of v<sub>GS</sub> required to form a conducting channel between drain and source and is between 0.3 and 0.6V<sup>2</sup>

- field-effect —when positive v<sub>GS</sub> is applied, an electric field develops between the gate electrode and induced n-channel – the conductivity of this channel is affected by the strength of field. The SiO<sub>2</sub> layer acts as dielectric

- The difference between v<sub>GS</sub> applied and V<sub>t</sub> is termed the effective voltage or the overdrive voltage and is the quantity that determines the charge in the channel. It is noted as shown in Equation (1)

$$v_{GS} - Vt \equiv v_{ov}$$

(1)

<sup>1</sup>do not confuse  $V_t$  with  $V_T$ —The latter is used to denote the thermal voltage VT <sup>2</sup> $V_{th}$  is used for n-type MOSFET and  $V_{tp}$  is used for p-channel MINIMUM VIEW FOR THE VIEW OF STORE 4.125

## Creating a channel for current flow

- A conducting channel forms a parallel plate capacitor with the gate

- The charge Q created in the charge is given by Equation (2) and Equation (3)

$$Q = CV$$

(2)

$$|Q| = C_g \cdot v_{OV} \tag{3}$$

Where the gate capacitor is given by Equation (4)

$$C_g = C_{ox} WL \tag{4}$$

June 29, 2022 9 / 25

Where:

Kizito NKURIKIYEYEZU, Ph.D

$C_{ox}$  is the capacitance per unit are *WL* is the area of the electrode

# Creating a channel for current flow

Since the parallel plate capacitor is given by expressed by the area A and the distance d between the plates Equation (5)

$$C = \frac{\epsilon A}{d} \tag{5}$$

Then, the oxide capacitance (Cox) (i.e., the capacitance of the parallel plate capacitor per unit gate area (F / m<sup>2</sup>)) is given by

$$C_{ox} = \epsilon_{ox} / t_{ox}$$

(6)

10/25

where:

Kizito NKURIKIYEYEZU, Ph.D.

$\varepsilon_{\textit{ox}}$  is the permittivity of the silicon dioxide

$$\varepsilon_{ox} = 3.45 \times 10^{-11} F/m$$

$t_{ox}$  = is the thickness of the silicon layer  $SiO_2$

- The voltage across the silicon layer must exceed V<sub>t</sub> for the n-channel to form

- As  $v_{ov}$  grows, so does the depth of the n-channel as well as

| MOSFETs | June 29 |

|---------|---------|

|         |         |

# Small v<sub>DS</sub> Model

# Small v<sub>DS</sub> Model for MOSFET

What is the current  $i_D$  For small values of  $v_{DS}$  (i.e., 50 mV or so)?

The charge of the parallel plate capacitor between the gate and the channel is given by Equation (8)

$$Q = CV$$

$$Q| = C_{ox} W L v_{OV} \quad (8)$$

The charge per unit length Q<sub>n</sub> is then given by Equation (9)

FIG 6. An NMOS transistor with  $v > V_t$ and with a small  $v_{DS}$  applied. The device acts as a resistance whose value is determined by  $v_{GS}$ . Specifically, the channel conductance is proportional to  $v_{GS} - V_t$ , and thus  $i_D$ is proportional to  $(v_{GS} - V_t)v_{DS}$ .

# Small V<sub>DS</sub> Model for MOSFET

Then the electric field along the channel is given by Equation (10)

$$|E| = \frac{v_{DS}}{L} \qquad (10)$$

The drift velocity of the electrons is given by Equation (11)

$$V_{drift} = \mu_n |E|$$

=  $\mu_n \frac{v_{DS}}{L}$

$\begin{array}{c} \begin{array}{c} & & & & & & \\ & & & & & \\ \hline & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ &$

**FIG 7.** An NMOS transistor with  $v > V_t$ and with a small  $v_{DS}$  applied. The device acts as a resistance whose value is determined by  $v_{GS}$ .

(11) Specifically, the channel conductance is proportional to v<sub>GS</sub> - Vt, and thus i<sub>D</sub> is proportional to (v<sub>GS</sub> - V<sub>t</sub>)v<sub>DS</sub>.

#### Kizito NKURIKIYEYEZU, Ph.D.

Kizito NKURIKIYEYEZU, Ph.D.

MOSFETs

une 29, 2022 12 / 25

# Small V<sub>DS</sub> Model for MOSFET

For small v<sub>DS</sub>, we can assume that the voltage between the gate and various points along the channel is equal to v<sub>GS</sub>. i<sub>D</sub> is given by Equation (12)<sup>2</sup>

$$\begin{split} i_{D} &= \mathcal{Q}_{n} \mathbf{v}_{drift} \\ &= \mathcal{C}_{ox} W \mathbf{v}_{OV} \mu_{n} \frac{\mathbf{v}_{DS}}{\mathbf{v}} \\ &= \begin{bmatrix} \mu_{n} \mathcal{C}_{ox} \left( \frac{W}{L} \right) \mathbf{v}_{ov} \end{bmatrix} \mathbf{v}_{DS} \\ &= \begin{bmatrix} \mu_{n} \mathcal{C}_{ox} \left( \frac{W}{L} \right) (\mathbf{v}_{GS} - \mathbf{V}_{l}) \end{bmatrix} \mathbf{v}_{DS} \end{split}$$

(12)

■ The conductance is given by Equation (13)

$$g_{DS} = \mu_n C_{ox} \left(\frac{W}{L}\right) v_{OV} = \mu_n C_{ox} \left(\frac{W}{L}\right) (v_{GS} - V_t)$$

(13)

See details in the textbook on page 253

June 29, 2022

13/25

#### Kizito NKURIKIYEYEZU, Ph.D

#### MOSFETs Ju

ine 29, 2022 14 / 25

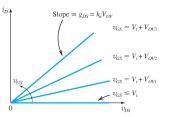

# Small V<sub>DS</sub> Model for MOSFET

- The factor  $k'_n = \mu_n C_{ox}$  is called the process transconductance and is affected by the type of manufacturing process

- The ratio of the width W to the length L (i.e., W/L) affects the conductance. For example, in the recent 5nm lithography technology process, the channel length L cannot be smaller than 5nm.

- A MOSFET transconductance parameter is given by

$$k_n = k'_n \frac{W}{L} = \mu_n C_{ox} \frac{W}{L} \tag{14}$$

The conductance depends on v<sub>GS</sub>

$$DS = 1/g_{DS} = 1/\mu_n C_{ox}(w/L) v_{OV} = \frac{1}{\mu_n C_{ox}(w/L)(v_{OS}-V)}$$

(15)

# Large v<sub>DS</sub> Model

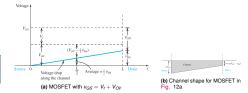

#### FIG 8. MOSFET operations for various values of Vos

A MOSFET is a voltage-controlled resistance. The slope of the curve which is  $a_{DS}$  is dependent on  $v_{QS}$  since  $V_{QV} = v_{QS} - V_t$ . When the voltage applied between drain and source, vos, is kept small, the device operates as a linear resistance whose value is controlled by vGS.

Kizito NKURIKIYEYEZU, Ph D

### MOSEET Large *v*<sub>DS</sub> Model of a MOSFET

- Different v<sub>GS</sub> will draw different amount of n carrier into the channel creating a non-uniform depth of the channel as shown in Fig. 9

- The channel depth is proportional to  $v_{GS}$  at the source end or

FIG 9. Operation of an NMOS transistor as vDS is increased. Note that an unequal channel depth is induced when a larger vos is applied across the transistor giving rise to non-uniform channel depth

### Large $v_{DS}$ Model of a MOSFET

The channel depth is proportional to VGD at the drain end or

$$v_{GD} = V_t + V_{OV} - vDS$$

FIG 10. Operation of an NMOS transistor as vos is increased. Note that an unequal channel depth is induced when a larger vos is applied across the transistor giving rise to non-uniform channel depth

| Kizito | NKURI | KIYEY | EZULI | Ph.D. |

|--------|-------|-------|-------|-------|

|        |       |       |       |       |

Kizito NKURIKIYEYEZU, Ph.D

# Non-linearity explanation

- When *v<sub>DS</sub>* increases beyond "small values", the relationship between *i<sub>D</sub>* and *v<sub>DS</sub>* ceases to be linear.

- Explanation:

- step1 Assume that v<sub>GS</sub> is held constant at value greater than V<sub>t</sub>.

- step2 Also assume that v<sub>DS</sub> is applied and appears as voltage drop across n-channel.

- step3 Note that voltage decreases from v<sub>GS</sub> at the source end of channel NKIBIKYYEZU Ph D MOSET

FIG 11. Operation of an NMOS transistor as  $v_{DS}$  is increased. Note the unequal channel depth due to a larger  $v_{DS}$  is applied across the transistor giving rise to non-uniform channel depth.

FIG 12. Linear proportionality of the channel depth of a MOSFET

Kizito NKURIKIYEYEZU, Ph D

In Fig. 12a, when  $\nu_{GS}=V_{1}+V_{OV}$ , applying  $\nu_{DS}$  causes the voltage drop along the channel to vary linearly, with an average value of  $1/2\nu_{DS}$  at the midpoint. Since  $\nu_{QD}>V_{1}$ , the channel still exists at the drain end. Fig. 12b shows the channel shape corresponding to the situation in Fig. 12a. While the depth of the channel at the source end is still proportional to  $V_{OV}$ , that at the drain end frain end frain end. Fig.

June 29, 2022

19/25

# Non-linearity explanation

- step4 Define *i*<sub>DS</sub> in terms of *v*<sub>DS</sub> and *v*<sub>OV</sub>.

- Without tapering of the charge, if v<sub>OV</sub> is independent of x, the area under the curve is vOVL. But with tapering, by using the area of a trapezoid, this area evaluates to (V<sub>OV</sub> 1/2v<sub>DS</sub>)L

- Previously, we saw that i<sub>D</sub> is defined by Equation (19)

Since now  $v_{OV} = v_{GS} - V_t$ , then Equation (19) becomes

$$i_{D} = \mu_{n} C_{ox} \frac{W}{L} \left[ (v_{GS} - V_{t}) v_{DS} - \frac{1}{2} v_{DS}^{2} \right]$$

$$= k_{n}' \frac{W}{L} \left[ (v_{GS} - V_{t}) v_{DS} - \frac{1}{2} v_{DS}^{2} \right]$$

(20)

Notice that when v<sub>DS</sub> is small, the quadratic term can be dropped and we end up with the small v<sub>DS</sub> equation.

MOSFETs

| Kizito N | KURIK | IYEYE | ZU. Ph. | D. |

|----------|-------|-------|---------|----|

|          |       |       |         |    |

# **Operation for** $v_{DS} \ge v_{OV}$

### Channel Pinch-Off and Current Saturation

FIG 13. Operation of MOSFET with  $v_{GS} = V_1 + V_{QV}$ When  $v_{DS} = V_{QV}$ , at the drain end,  $v_{GD}$  decreases to  $V_1$  and the channel depth at the drain end reduces to zero (pinch-off). At this point, the MOSFET enters the saturation mode of operation. Further increasing  $v_{DS}$  has no effect on the channel shape and  $i_0$  remains constant.

# Channel Pinch-Off and Current Saturation

- $\blacksquare$  When  $v_{DS} = V_{OV}$  , then the channel depth is zero near the drain end

- At this junction, increasing v<sub>DS</sub> does not increase the drain current i<sub>D</sub>

$$i_{Dsat} = \frac{1}{2} k' \frac{W}{L} V_{OV}^2 \tag{21}$$

The saturation voltage is given by

$$V_{DSsat} = V_{OV} = V_{GS} - V_t \tag{22}$$

In general, as a function of v<sub>OV</sub>, in the saturation region,

$$i_{D} = \frac{1}{2} k'_{n} \frac{W}{L} v_{OV}^{2}$$

=  $\frac{1}{2} k'_{n} \frac{W}{L} (v_{GS} - V_{t})^{2}$  (23)

■ In the saturation region, the relation between i<sub>DS</sub> and v<sub>GS</sub> is nonlinear.

NMOS transistor operated with  $v_{GS} = V_t + V_{OV}$

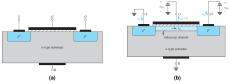

# The p-Channel MOSFET

A PMOS can be made by replacing p region with n region and vice versa

#### FIG 15. Physical structure of the PMOS transistor

Note that it is similar to the NMOS transistor except that all semiconductor regions are reversed in polarity. Fig. 15b shows the effect of a negative voltage  $v_{GS}$  of magnitude greater than  $V_{IP}$ . This negative voltage induces a p-channel, and a negative  $v_{DS}$  causes a current *i*<sub>D</sub> to flow from source

# The complementary MOS of CMOS

CMOS employs MOS transistors of both polarities.

- more difficult to fabricate

- more powerful and flexible

- now more prevalent than NMOS or PMOS

#### FIG 16. Cross section of a CMOS integrated circuit.

Note that the PMOS transistor is formed in a separate n-type region, known as an n well. Another arrangement is also possible in which an n-type substrate (body) is used and the n device is formed in a p well. Not shown are the connections made to the p-type body and to the n well; the latter functions as the body terminal for the p-channel device.

| Kizito NKURIKIYEYEZU, Ph.D. | MOSFETs | June 29, 2022 | 24 / 25 | Kizito NKURIKIYEYEZU, Ph.D. | MOSFETs | June 29, 2022 | 25 / 25 |

|-----------------------------|---------|---------------|---------|-----------------------------|---------|---------------|---------|

|                             |         |               |         |                             |         |               |         |

|                             |         |               |         |                             |         |               |         |

|                             |         |               |         |                             |         |               |         |

|                             |         |               |         |                             |         |               |         |

|                             |         |               |         |                             |         |               |         |

|                             |         |               |         |                             |         |               |         |

|                             |         |               |         |                             |         |               |         |

|                             |         |               |         |                             |         |               |         |

|                             |         |               |         |                             |         |               |         |

|                             |         |               |         |                             |         |               |         |

|                             | End     |               |         |                             |         |               |         |

|                             | End     |               |         |                             |         |               |         |

|                             |         |               |         |                             |         |               |         |

|                             |         |               |         |                             |         |               |         |

|                             |         |               |         |                             |         |               |         |

|                             |         |               |         |                             |         |               |         |

|                             |         |               |         |                             |         |               |         |

|                             |         |               |         |                             |         |               |         |

|                             |         |               |         |                             |         |               |         |

|                             |         |               |         |                             |         |               |         |